# Quad, Serial-Input 12-Bit/10-Bit DACs

# AD7398/AD7399

#### **FEATURES**

AD7398—12-bit resolution

AD7399—10-bit resolution

Programmable power shutdown

Single (3 V to 5 V) or dual (±5 V) supply operation

3-wire, serial SPI®-compatible interface

Internal power-on reset

Double buffered registers for simultaneous

multichannel DAC update

Four separate rail-to-rail reference inputs

Thin profile, TSSOP-16 package available

Low tempco: 1.5 ppm/°C

Qualified for automotive applications

#### **APPLICATIONS**

Automotive output voltage span Portable communications Digitally controlled calibration PC peripherals

#### **GENERAL DESCRIPTION**

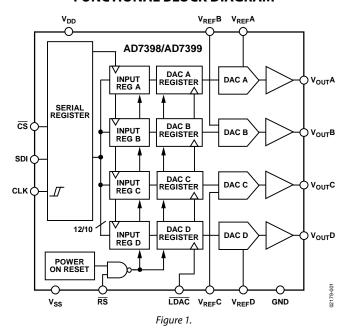

The AD7398/AD7399 family of quad, 12-bit/10-bit, voltage output digital-to-analog converters (DACs) is designed to operate from a single 3 V to 5 V supply or a dual ±5 V supply. Built with the Analog Devices, Inc. robust CBCMOS process, these monolithic DACs offer the user low cost with ease-of-use in single or dual-supply systems.

The applied external reference,  $V_{\text{REF}}$ , determines the full-scale output voltage. Valid  $V_{\text{REF}}$  values include  $V_{\text{SS}} < V_{\text{REF}} < V_{\text{DD}}$  that result in a wide selection of full-scale outputs. For multiplying applications, ac inputs can be as large as  $\pm 5~V_{\text{P}}.$

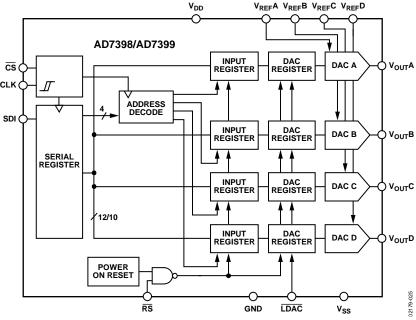

A doubled-buffered serial-data interface offers high speed, 3-wire, SPI- and microcontroller-compatible inputs using serial data-in (SDI), clock (CLK), and a chip-select  $\overline{(CS)}$ . A common level-sensitive, load-DAC strobe  $\overline{(LDAC)}$  input allows simultaneous update of all DAC outputs from previously loaded input registers. Additionally, an internal power-on reset forces the output voltage to zero at system turn on. An external asynchronous reset  $\overline{(RS)}$  also forces all registers to the zero code state. A programmable power-shutdown feature reduces power dissipation on unused DACs.

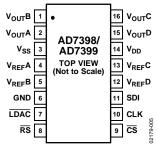

#### **FUNCTIONAL BLOCK DIAGRAM**

Both parts are offered in the same pinout, enabling users to select the appropriate resolution for their application without

redesigning the layout. For 8-bit resolution applications, see the pin-compatible AD7304 product.

The AD7398/AD7399 are specified over the extended industrial  $(-40^{\circ}\text{C to} + 125^{\circ}\text{C})$  temperature range. Parts are available in 16-lead, wide body SOIC and ultracompact, thin, 1.1 mm TSSOP packages.

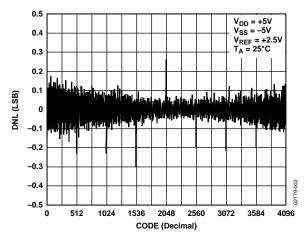

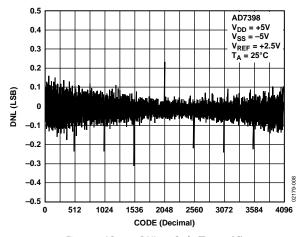

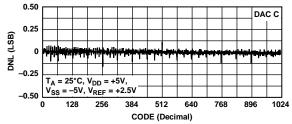

Figure 2. AD7398 DNL vs. Code ( $T_A = 25$ °C)

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features                                    | 1 |

|---------------------------------------------|---|

| Applications                                | 1 |

| Functional Block Diagram                    | 1 |

| General Description                         | 1 |

| Revision History                            | 2 |

| Specifications                              | 3 |

| AD7398 12-Bit Voltage Output DAC            | 3 |

| AD7399 10-Bit Voltage Output DAC            | 4 |

| Timing Diagrams                             | 5 |

| Absolute Maximum Ratings                    | 6 |

| ESD Caution                                 | 6 |

| Pin Configuration And Function Descriptions | 7 |

| Input Registers                             | 8 |

| AD7398 Serial Input Register Data Format    | 8 |

| AD7399 Serial Input Register Data Format    | 8 |

| Terminology                                 | 9 |

|                                             |   |

|                                             |   |

| ypical Performance Characteristics                  | 10 |

|-----------------------------------------------------|----|

| Theory of Operation                                 | 14 |

| DAC Operation                                       | 14 |

| Operation with V <sub>REF</sub> Equal to the Supply | 15 |

| Power Supply Sequencing                             | 15 |

| Programmable Power Shutdown                         | 15 |

| Worst Case Accuracy                                 | 15 |

| Serial Data Interface                               | 15 |

| Power-On Reset                                      | 16 |

| Microprocessor Interfacing                          | 16 |

| Applications Information                            | 18 |

| Staircase Windows Comparator                        | 18 |

| Programmable DAC Reference Voltage                  | 19 |

| Outline Dimensions                                  | 20 |

| Ordering Guide                                      | 21 |

| REVISION HISTORY                                                |            |

|-----------------------------------------------------------------|------------|

| 1/11—Rev. B to Rev. C<br>Added Automotive Model and Information | Throughout |

| 12/09—Rev. A to Rev. B                                          |            |

| Changes to Ordering Guide                                       | 21         |

| 6/06—Rev. 0 to Rev. A                                           |            |

| Updated Format                                                  | Universal  |

| Changes to Table 1                                              | 3          |

| Changes to Table 2                                              | 4          |

| Changes to Ordering Guide                                       | 21         |

11/00—Revision 0: Initial Version

# **SPECIFICATIONS**

## **AD7398 12-BIT VOLTAGE OUTPUT DAC**

$V_{\text{DD}} = 5 \text{ V}, V_{\text{SS}} = 0 \text{ V}; \text{ or } V_{\text{DD}} = +5 \text{ V}, V_{\text{SS}} = -5 \text{ V}, V_{\text{REF}} = +2.5 \text{ V}, -40 ^{\circ}\text{C} < T_{\text{A}} < +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$

Table 1.

| Parameter                              | Symbol                             | Condition                                                                 | 3 V to 5 V ± 10%      | ±5 V ± 10%            | Unit                |

|----------------------------------------|------------------------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|---------------------|

| STATIC PERFORMANCE                     |                                    |                                                                           |                       |                       |                     |

| Resolution <sup>1</sup>                | N                                  |                                                                           | 12                    | 12                    | Bits                |

| Relative Accuracy <sup>2</sup>         | INL                                |                                                                           | ±1.5                  | ±1.5                  | LSB max             |

| Differential Nonlinearity <sup>2</sup> | DNL                                | Monotonic                                                                 | ±1                    | ±1                    | LSB max             |

| Zero-Scale Error                       | $V_{ZSE}$                          | Data = 000 <sub>H</sub>                                                   | 7                     | ±2.5                  | mV max              |

| Full-Scale Voltage Error               | $V_{FSE}$                          | Data = FFF <sub>H</sub>                                                   | ±2.5                  | ±2.5                  | mV max              |

| Full-Scale Tempco <sup>3</sup>         | $TCV_FS$                           |                                                                           | 1.5                   | 1.5                   | ppm/°C typ          |

| REFERENCE INPUT                        |                                    |                                                                           |                       |                       |                     |

| V <sub>REF</sub> IN Range <sup>4</sup> | $V_{REF}$                          |                                                                           | 0/V <sub>DD</sub>     | $V_{SS}/V_{DD}$       | V min/max           |

| Input Resistance⁵                      | $R_{REF}$                          | Data = 555 <sub>H</sub> , worst case                                      | 35                    | 35                    | kΩ typ <sup>6</sup> |

| Input Capacitance <sup>3</sup>         | C <sub>REF</sub>                   |                                                                           | 5                     | 5                     | pF typ              |

| ANALOG OUTPUT                          |                                    |                                                                           |                       |                       |                     |

| Output Voltage Range                   | V <sub>OUT</sub>                   |                                                                           | 0 to V <sub>REF</sub> | 0 to V <sub>REF</sub> | V                   |

| Output Current                         | I <sub>OUT</sub>                   | Data = $800_H$ , $\Delta V_{OUT} = 4 LSBs$                                | ±5                    | ±5                    | mA typ              |

| Capacitive Load <sup>3</sup>           | CL                                 | No oscillation                                                            | 200                   | 400                   | pF max              |

| LOGIC INPUTS                           |                                    |                                                                           |                       |                       |                     |

| Logic Input Low Voltage                | V <sub>IL</sub>                    | $V_{DD} = 3 V$                                                            | 0.5                   |                       | V max               |

|                                        |                                    | $V_{DD} = 5 V$                                                            | 0.8                   | 0.8                   | V max               |

| Logic Input High Voltage               | V <sub>IH</sub>                    | CLK only                                                                  | 80% V <sub>DD</sub>   | 4.0                   | V min               |

|                                        |                                    |                                                                           | 2.1 to 2.4            | 2.4                   | V min               |

| Input Leakage Current                  | I <sub>IL</sub>                    |                                                                           | 1                     | 1                     | μA max              |

| Input Capacitance <sup>3</sup>         | C <sub>IL</sub>                    |                                                                           | 10                    | 10                    | pF max              |

| INTERFACE TIMING <sup>3, 7</sup>       |                                    |                                                                           |                       |                       |                     |

| Clock Frequency                        | f <sub>CLK</sub>                   |                                                                           | 11                    | 16.6                  | MHz max             |

| Clock Width High                       | t <sub>CH</sub>                    |                                                                           | 45                    | 30                    | ns min              |

| Clock Width Low                        | <b>t</b> <sub>CL</sub>             |                                                                           | 45                    | 30                    | ns min              |

| CS to Clock Setup                      | t <sub>CSS</sub>                   |                                                                           | 10                    | 5                     | ns min              |

| Clock to CS Hold                       | t <sub>CSH</sub>                   |                                                                           | 20                    | 15                    | ns min              |

| Load DAC Pulse Width                   | t <sub>LDAC</sub>                  |                                                                           | 45                    | 30                    | ns min              |

| Data Setup                             | t <sub>DS</sub>                    |                                                                           | 15                    | 10                    | ns min              |

| Data Hold                              | t <sub>DH</sub>                    |                                                                           | 10                    | 5                     | ns min              |

| Load Setup to CS                       | t <sub>LDS</sub>                   |                                                                           | 0                     | 0                     | ns min              |

| Load Hold to CS                        | t <sub>LDH</sub>                   |                                                                           | 20                    | 15                    | ns min              |

| AC CHARACTERISTICS                     |                                    |                                                                           |                       |                       |                     |

| Output Slew Rate                       | SR                                 | Data = $000_{H}$ to $FFF_{H}$ to $000_{H}$                                | 2                     | 2                     | V/µs typ            |

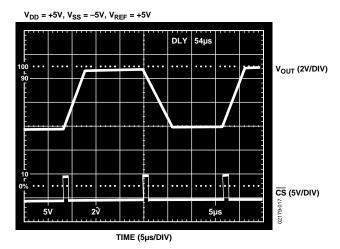

| Settling Time <sup>8</sup>             | ts                                 | To ±0.1% of full scale                                                    | 6                     | 6                     | μs typ              |

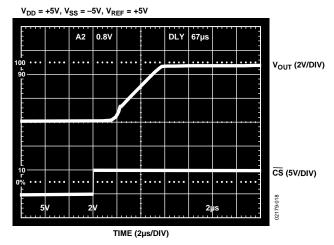

| Shutdown Recovery                      | t <sub>SDR</sub>                   |                                                                           | 6                     | 6                     | μs typ              |

| DAC Glitch                             | Q                                  | Code 7FF <sub>H</sub> to 800 <sub>H</sub> to 7FF <sub>H</sub>             | 150                   | 150                   | nVs typ             |

| Digital Feedthrough                    | Q <sub>DF</sub>                    |                                                                           | 15                    | 15                    | nVs typ             |

| Feedthrough                            | V <sub>OUT</sub> /V <sub>REF</sub> | $V_{REF} = 1.5 V_{DC} 1 V p-p$ , data = 000 <sub>H</sub> ,<br>f = 100 kHz | -63                   | -63                   | dB typ              |

| Parameter                | Symbol             | Condition                                                                            | 3 V to 5 V ± 10% | ±5 V ± 10% | Unit       |

|--------------------------|--------------------|--------------------------------------------------------------------------------------|------------------|------------|------------|

| SUPPLY CHARACTERISTICS   |                    |                                                                                      |                  |            |            |

| Shutdown Supply Current  | I <sub>DD_SD</sub> | No load                                                                              | 30/60            | 30/60      | μΑ typ/max |

| Positive Supply Current  | I <sub>DD</sub>    | $V_{IL} = 0 \text{ V, no load, } -40^{\circ}\text{C} < T_{A} < +125^{\circ}\text{C}$ | 1.5/2.8          | 1.6/3      | mA typ/max |

|                          | $I_{DD}$           | $V_{IL} = 0 \text{ V, no load, } -40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$    | 1.5/2.6          | 1.6/2.8    | mA typ/max |

| Negative Supply Current  | Iss                | $V_{IL} = 0 V$ , no load                                                             | 1.5/2.5          | 1.6/2.7    | mA typ/max |

| Power Dissipation        | P <sub>DISS</sub>  | V <sub>IL</sub> = 0 V, no load                                                       | 5                | 16         | mW typ     |

| Power Supply Sensitivity | PSS                | $\Delta V_{DD} = \pm 5\%$                                                            | 0.006            | 0.006      | %/% max    |

$<sup>^{1}</sup>$  One LSB =  $V_{REF}/4096 V$  for the 12-bit AD7398.

#### **AD7399 10-BIT VOLTAGE OUTPUT DAC**

$V_{DD} = 5 \text{ V}, V_{SS} = 0 \text{ V}; \text{ or } V_{DD} = +5 \text{ V}, V_{SS} = -5 \text{ V}; V_{REF} = +2.5 \text{ V}, -40 ^{\circ}\text{C} < T_{A} < +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$

Table 2.

| Parameter                              | Symbol            | Condition                                 | 3 V to 5 V ± 10%      | ±5 V ± 10%            | Unit                |

|----------------------------------------|-------------------|-------------------------------------------|-----------------------|-----------------------|---------------------|

| STATIC PERFORMANCE                     |                   |                                           |                       |                       |                     |

| Resolution <sup>1</sup>                | N                 |                                           | 10                    | 10                    | Bits                |

| Relative Accuracy <sup>2</sup>         | INL               |                                           | ±1                    | ±1                    | LSB max             |

| Differential Nonlinearity <sup>2</sup> | DNL               | Monotonic                                 | ±1                    | ±1                    | LSB max             |

| Zero-Scale Error                       | $V_{ZSE}$         | Data = 000 <sub>H</sub>                   | 7                     | ±4                    | mV max              |

| Full-Scale Voltage Error               | $V_{FSE}$         | Data = 3FF <sub>H</sub>                   | ±15                   | ±15                   | mV max              |

| Full-Scale Tempco <sup>3</sup>         | TCV <sub>FS</sub> |                                           | 1.5                   | 1.5                   | ppm/°C typ          |

| REFERENCE INPUT                        |                   |                                           |                       |                       |                     |

| V <sub>REF</sub> IN Range⁴             | $V_{REF}$         |                                           | 0/V <sub>DD</sub>     | $V_{SS}/V_{DD}$       | V min/max           |

| Input Resistance <sup>5</sup>          | R <sub>REF</sub>  | Data = 155 <sub>H</sub> , worst case      | 40                    | 40                    | kΩ typ <sup>6</sup> |

| Input Capacitance <sup>3</sup>         | C <sub>REF</sub>  |                                           | 5                     | 5                     | pF typ              |

| ANALOG OUTPUT                          |                   |                                           |                       |                       |                     |

| Output Voltage Range                   | V <sub>OUT</sub>  |                                           | 0 to V <sub>REF</sub> | 0 to V <sub>REF</sub> | V                   |

| Output Current                         | louт              | Data = $200_H$ , $\Delta V_{OUT} = 1$ LSB | ±5                    | ±5                    | mA typ              |

| Capacitive Load <sup>3</sup>           | $C_L$             | No oscillation                            | 200                   | 400                   | pF max              |

| LOGIC INPUTS                           |                   |                                           |                       |                       |                     |

| Logic Input Low Voltage                | VIL               | $V_{DD} = 3 V$                            | 0.5                   |                       | V max               |

|                                        |                   | $V_{DD} = 5 V$                            | 0.8                   | 0.8                   | V max               |

| Logic Input High Voltage               | V <sub>IH</sub>   | CLK only                                  | 80% V <sub>DD</sub>   | 4.0                   | V min               |

|                                        |                   |                                           | 2.1 to 2.4            | 2.4                   | V min               |

| Input Leakage Current                  | I <sub>IL</sub>   |                                           | 1                     | 1                     | μA max              |

| Input Capacitance <sup>3</sup>         | C <sub>IL</sub>   |                                           | 10                    | 10                    | pF max              |

| INTERFACE TIMING <sup>3, 7</sup>       |                   |                                           |                       |                       |                     |

| Clock Frequency                        | f <sub>CLK</sub>  |                                           | 11                    | 16.6                  | MHz max             |

| Clock Width High                       | t <sub>CH</sub>   |                                           | 45                    | 30                    | ns min              |

| Clock Width Low                        | t <sub>CL</sub>   |                                           | 45                    | 30                    | ns min              |

| CS to Clock Setup                      | tcss              |                                           | 10                    | 5                     | ns min              |

| Clock to CS Hold                       | t <sub>CSH</sub>  |                                           | 20                    | 15                    | ns min              |

| Load DAC Pulse Width                   | t <sub>LDAC</sub> |                                           | 45                    | 30                    | ns min              |

| Data Setup                             | t <sub>DS</sub>   |                                           | 15                    | 10                    | ns min              |

| Data Hold                              | t <sub>DH</sub>   |                                           | 10                    | 5                     | ns min              |

| Load Setup to $\overline{CS}$          | t <sub>LDS</sub>  |                                           | 0                     | 0                     | ns min              |

| Load Hold to CS                        | t <sub>LDH</sub>  |                                           | 20                    | 15                    | ns min              |

$<sup>^2</sup>$  The first eight codes (000 $_{\rm H}$  to 007 $_{\rm H}$ ) are excluded from the linearity error measurement in single-supply operation.

<sup>&</sup>lt;sup>3</sup> These parameters are guaranteed by design and not subject to production testing.

<sup>&</sup>lt;sup>4</sup> When  $\dot{V}_{REF}$  is connected to either the  $\dot{V}_{DD}$  or the  $\dot{V}_{SS}$  power supply, the corresponding  $\dot{V}_{OUT}$  voltage programs between ground and the supply voltage minus the offset voltage of the output buffer, which is the same as the  $\dot{V}_{ZSE}$  error specification. See additional information in the Theory of Operation section.

<sup>&</sup>lt;sup>5</sup> Input resistance is code dependent.

<sup>&</sup>lt;sup>6</sup> Typicals represent average readings measured at 25°C.

<sup>&</sup>lt;sup>7</sup> All input control signals are specified with  $t_R = t_F = 2$  ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V.

<sup>&</sup>lt;sup>8</sup> The settling time specification does not apply for negative going transitions within the last 3 LSBs of ground.

| Parameter                      | Symbol            | Condition                                                           | 3 V to 5 V ± 10% | ±5 V ± 10% | Unit       |

|--------------------------------|-------------------|---------------------------------------------------------------------|------------------|------------|------------|

| AC CHARACTERISTICS             |                   |                                                                     |                  |            |            |

| Output Slew Rate               | SR                | Data = $000_H$ to $3FF_H$ to $000_H$                                | 2                | 2          | V/μs typ   |

| Settling Time <sup>8</sup>     | ts                | To ±0.1% of full scale                                              | 6                | 6          | μs typ     |

| Shutdown Recovery              | t <sub>SDR</sub>  |                                                                     | 6                | 6          | μs typ     |

| DAC Glitch                     | Q                 | Code 1FF <sub>H</sub> to 200 <sub>H</sub> to 1FF <sub>H</sub>       | 150              | 150        | nVs typ    |

| Digital Feedthrough            | $Q_{DF}$          |                                                                     | 15               | 15         | nVs typ    |

| Feedthrough                    | $V_{OUT}/V_{REF}$ | $V_{REF} = 1.5 V_{DC} + 1 V p-p,$                                   | -63              | -63        | dB typ     |

|                                |                   | data = 000 <sub>H</sub> , f = 100 kHz                               |                  |            |            |

| SUPPLY CHARACTERISTICS         |                   |                                                                     |                  |            |            |

| Shutdown Supply Current IDD_SD |                   | No load                                                             | 30/60            | 30/60      | μΑ typ/max |

| Positive Supply Current        | I <sub>DD</sub>   | $V_{IL} = 0 \text{ V, no load,}$<br>-40°C < T <sub>A</sub> < +125°C | 1.5/2.8          | 1.6/3      | mA typ/max |

|                                | I <sub>DD</sub>   | $V_{IL} = 0 \text{ V, no load,}$<br>-40°C < T <sub>A</sub> < +85°C  | 1.5/2.6          | 1.6/2.8    | mA typ/max |

| Negative Supply Current        | Iss               | V <sub>IL</sub> = 0 V, no load                                      | 1.5/2.5          | 1.6/2.7    | mA typ/max |

| Power Dissipation              | P <sub>DISS</sub> | V <sub>IL</sub> = 0 V, no load                                      | 5                | 16         | mW typ     |

| Power Supply Sensitivity       | PSS               | $\Delta V_{DD} = \pm 5\%$                                           | 0.006            | 0.006      | %/% max    |

$<sup>^{1}</sup>$  One LSB =  $V_{REF}/1024 V$  for the 10-bit AD7399.

#### **TIMING DIAGRAMS**

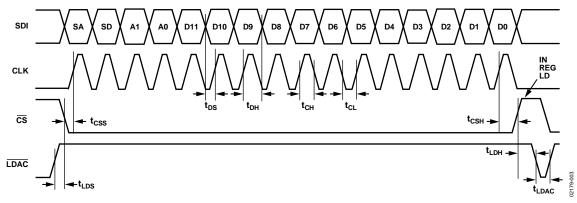

Figure 3. AD7398 Timing Diagram (AD7399 with SDI = 14 Bits Only)

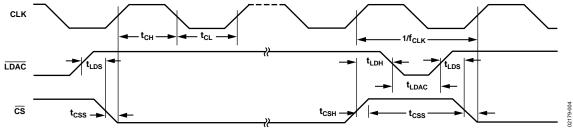

Figure 4. Continuous Clock Timing Diagram

$<sup>^2</sup>$  The first two codes (000<sub>H</sub> and 001<sub>H</sub>) are excluded from the linearity error measurement in single-supply operation.

<sup>&</sup>lt;sup>3</sup> These parameters are guaranteed by design and not subject to production testing.

$<sup>^4</sup>$  When  $\dot{V}_{REF}$  is connected to either the  $\dot{V}_{DD}$  or the  $V_{SS}$  power supply, the corresponding  $V_{OUT}$  voltage programs between ground and the supply voltage minus the offset voltage of the output buffer, which is the same as the  $V_{ZSE}$  error specification. See additional discussion in the Theory of Operation section.

<sup>&</sup>lt;sup>5</sup> Input resistance is code dependent.

<sup>&</sup>lt;sup>6</sup> Typicals represent average readings measured at 25°C.

<sup>7</sup> Åll input control signals are specified with  $t_R = t_F = 2$  ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V.

<sup>&</sup>lt;sup>8</sup> The settling time specification does not apply for negative going transitions within the last 3 LSBs of ground.

## **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Table 5.                                             |                                                        |

|------------------------------------------------------|--------------------------------------------------------|

| Parameter                                            | Rating                                                 |

| V <sub>DD</sub> to GND                               | −0.3 V, +7 V                                           |

| V <sub>ss</sub> to GND                               | +0.3 V, -7 V                                           |

| $V_{REF}$ to GND                                     | $V_{SS}$ , $V_{DD}$                                    |

| Logic Inputs to GND                                  | −0.3 V, +8 V                                           |

| V <sub>OUT</sub> to GND                              | $V_{SS} - 0.3 \text{ V}, V_{DD} + 0.3 \text{ V}$       |

| I <sub>OUT</sub> Short Circuit to GND                | 50 mA                                                  |

| Thermal Resistance ( $\theta_{JA}$ )                 |                                                        |

| 16-Lead SOIC_W Package<br>(RW-16)                    | 158°C/W                                                |

| 16-Lead TSSOP Package<br>(RU-16)                     | 180°C/W                                                |

| Maximum Junction<br>Temperature (T <sub>J</sub> Max) | 150℃                                                   |

| Package Power Dissipation                            | (T <sub>J</sub> Max – T <sub>A</sub> )/θ <sub>JA</sub> |

| Operating Temperature Range                          | -40°C to +125°C                                        |

| Storage Temperature Range                            | −65°C to +150°C                                        |

| Reflow Soldering Peak                                |                                                        |

| Temperature                                          |                                                        |

| SnPb                                                 | 240°C                                                  |

| Pb-Free                                              | 260°C                                                  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

#### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic           | Description                                                                                                                                                                          |

|---------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>оит</sub> В | DAC B Voltage Output.                                                                                                                                                                |

| 2       | VоитA              | DAC A Voltage Output.                                                                                                                                                                |

| 3       | V <sub>SS</sub>    | Negative Power Supply Input. Specified range of operation 0 V to $-5.5$ V.                                                                                                           |

| 4       | $V_{REF}A$         | DAC A Reference Voltage Input Terminal. Establishes DAC A full-scale output voltage. Pin can be tied to $V_{DD}$ pin or $V_{SS}$ pin.                                                |

| 5       | V <sub>REF</sub> B | DAC B Reference Voltage Input Terminal. Establishes DAC B full-scale output voltage. Pin can be tied to $V_{DD}$ pin or $V_{SS}$ pin.                                                |

| 6       | GND                | Ground Pin.                                                                                                                                                                          |

| 7       | LDAC               | Load DAC Register Strobe. Level sensitive active low. Transfers all input register data to DAC registers.  Asynchronous active low input. See Table 5 for operation.                 |

| 8       | RS                 | Resets Input and DAC Registers to All Zero Codes. Shift register contents unchanged.                                                                                                 |

| 9       | CS                 | Chip Select. Active low input. Disables shift register loading when high. Transfers serial register data to the input register when CS returns high. Does not effect LDAC operation. |

| 10      | CLK                | Schmitt Triggered Clock Input. Positive edge clocks data into shift register.                                                                                                        |

| 11      | SDI                | Serial Data Input. Input data loads directly into the shift register.                                                                                                                |

| 12      | V <sub>REF</sub> D | DAC D Reference Voltage Input Terminal. Establishes DAC D full-scale output voltage. Pin can be tied to $V_{DD}$ pin or $V_{SS}$ pin.                                                |

| 13      | V <sub>REF</sub> C | DAC C Reference Voltage Input Terminal. Establishes DAC C full-scale output voltage. Pin can be tied to $V_{DD}$ pin or $V_{SS}$ pin.                                                |

| 14      | V <sub>DD</sub>    | Positive Power Supply Input. Specified range of operation 3 V to 5 V $\pm$ 10%.                                                                                                      |

| 15      | V <sub>OUT</sub> D | DAC D Voltage Output.                                                                                                                                                                |

| 16      | V <sub>OUT</sub> C | DAC C Voltage Output.                                                                                                                                                                |

#### **Table 5. Control Logic Truth Table**

| CS         | CLK        | LDAC       | Serial Shift Register Function       | Input Register Function              | DAC Register |

|------------|------------|------------|--------------------------------------|--------------------------------------|--------------|

| Н          | Χ          | Н          | No effect                            | No effect                            | No effect    |

| L          | L          | Н          | No effect                            | No effect                            | No effect    |

| L          | <b>↑</b> + | Н          | Shift register data advanced one bit | Latched                              | No effect    |

| L          | Н          | Н          | No effect                            | Latched                              | No effect    |

| <b>†</b> + | L/H        | Н          | No effect                            | Updated with shift register contents | No effect    |

| Н          | Х          | L          | No effect                            | Latched                              | Transparent  |

| Н          | Х          | <b>↑</b> + | No effect                            | Latched                              | Latched      |

- 1.  $\uparrow$ + = Positive logic transition;  $\downarrow$  = Negative logic transition; X = Don't Care.

- 2. At power-on, both the input register and the DAC register are loaded with all zeros.

- 3. During power shutdown, reprogramming of any internal registers can take place, but the output amplifiers do not produce the new values until the part is taken out of shutdown mode.

- 4. The  $\overline{\text{LDAC}}$  input is a level-sensitive input that controls the four DAC registers.

## **INPUT REGISTERS**

#### **AD7398 SERIAL INPUT REGISTER DATA FORMAT**

Data is loaded in the MSB first format.

MSB LSB

| B15 | B14 | B13 | B12 | B11 | B10 | В9 | B8 | B7 | B6 | B5 | B4 | В3 | B2 | B1 | В0 |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| SA  | SD  | A1  | A0  | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

NOTE

Bit Position B14 and Bit Position B15 are the SD and SA power shutdown control bits. If SA is set to Logic 1, all DACs are placed in the power shutdown mode. If SD is set to Logic 1, the address decoded by Bit B12 and Bit B13 (A0 and A1) determine the DAC channel that is placed in the power shutdown state.

#### **AD7399 SERIAL INPUT REGISTER DATA FORMAT**

Data is loaded in the MSB first format.

**MSB LSB B13 B10** В8 **B12 B11** В9 **B7 B6 B5 B4** В3 **B2 B**1 **B0** SA SD **A**1 A0 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

NOTE

Bit Position B12 and Bit Position B13 are the SD and SA power shutdown control bits. If SA is set to Logic 1, all DACs are placed in the power shutdown mode. If SD is set to Logic 1, the address decoded by Bit B10 and Bit B11 (A0 and A1) determine the DAC channel that is placed in the power shutdown state.

#### Table 6. AD7398/AD7399 Address Decode Control

| SA | SD | A1 | A0 | DAC Channel Affected         |

|----|----|----|----|------------------------------|

| 1  | Х  | Х  | Х  | All DACs shutdown            |

| 0  | 1  | 0  | 0  | DAC A shutdown               |

| 0  | 1  | 0  | 1  | DAC B shutdown               |

| 0  | 1  | 1  | 0  | DAC C shutdown               |

| 0  | 1  | 1  | 1  | DAC D shutdown               |

| 0  | 0  | 0  | 0  | DAC A input register decoded |

| 0  | 0  | 0  | 1  | DAC B input register decoded |

| 0  | 0  | 1  | 0  | DAC C input register decoded |

| 0  | 0  | 1  | 1  | DAC D input register decoded |

### **TERMINOLOGY**

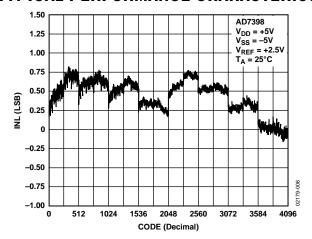

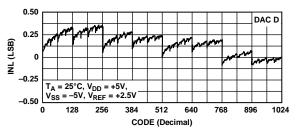

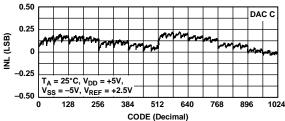

#### Relative Accuracy (INL)

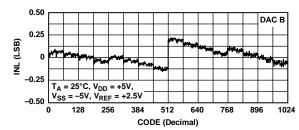

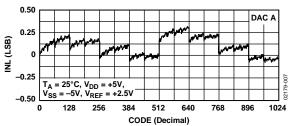

For the DAC, relative accuracy or integral nonlinearity (INL) is a measure of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. Figure 6 illustrates a typical INL vs. code plot.

#### Differential Nonlinearity (DNL)

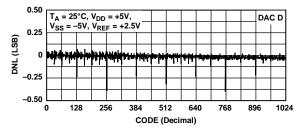

Differential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB maximum ensures monotonicity. Figure 8 illustrates a typical DNL vs. code plot.

#### Zero-Scale Error (V<sub>ZSE</sub>)

Zero-scale error is a measure of the output voltage error from zero voltage when zero code is loaded to the DAC register.

#### Full-Scale Error (V<sub>FSE</sub>)

Full-scale error is a measure of the output voltage error from full-scale voltage when full-scale code is loaded to the DAC register.

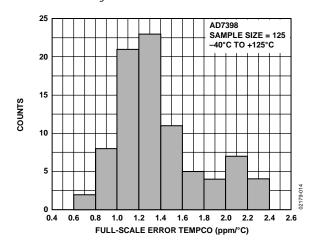

#### Full-Scale Temperature Coefficient (TC<sub>VFS</sub>)

This is a measure of the change in full-scale error with a change in temperature. It is expressed in ppm/°C or mV/°C.

#### DAC Glitch Impulse (Q)

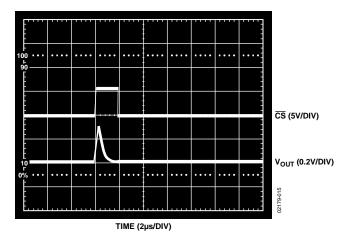

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is normally specified as the area of the glitch in nV s and is measured when the digital input code is changed by 1 LSB at the major carry transition (midscale transition). A plot of the glitch impulse is shown in Figure 15.

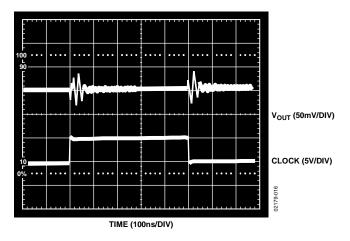

#### Digital Feedthrough (QDF)

Digital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital inputs of the DAC, but is measured when the DAC output is not updated.  $\overline{\text{CS}}$  is held high while the CLK and SDI signals are toggled. It is specified in nV-s, and is measured with a full-scale code change on the data bus, such as from all 0s to all 1s and vice versa. A typical plot of digital feedthrough is shown in Figure 16.

#### Power Supply Sensitivity (PSS)

This specification indicates how the output of the DAC is affected by changes in the power supply voltage. Power supply sensitivity is quoted in terms of % change in output per % change in  $V_{\rm DD}$  for full-scale output of the DAC.  $V_{\rm DD}$  is varied by  $\pm 10\%$ .

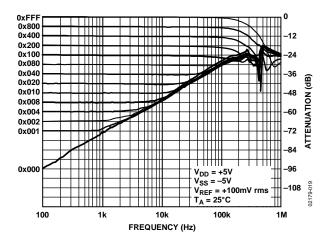

#### Reference Feedthrough (V<sub>OUT</sub>/V<sub>REF</sub>)

This is a measure of the feedthrough from the  $V_{\text{REF}}$  input to the DAC output when the DAC is loaded with all 0s. A 100 kHz, 1 V p-p is applied to  $V_{\text{REF}}.$  Reference feedthrough is expressed in dB or mV p-p.

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 6. AD7398 INL vs. Code ( $T_A = 25$ °C)

Figure 7. AD7399 INL vs. Code ( $T_A = 25$ °C)

Figure 8. AD7398 DNL vs. Code ( $T_A = 25$  °C)

Figure 9. AD7399 DNL vs. Code ( $T_A = 25$  °C)

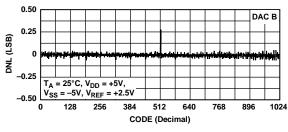

Figure 10. AD7398 INL, DNL, FSE vs. Reference Voltage

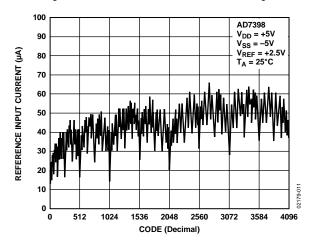

Figure 11. AD7398 Reference Input Current vs. Code

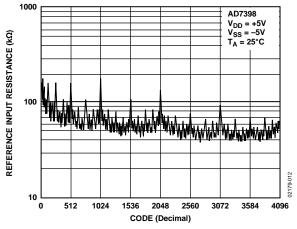

Figure 12. AD7398 Reference Input Resistance vs. Code

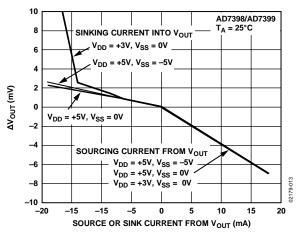

Figure 13. ΔV<sub>OUT</sub> vs. Load Current

Figure 14. AD7398 Full-Scale Error Tempco

Figure 15. AD7398 Midscale Glitch

Figure 16. AD7398 Digital Feedthrough

Figure 17. AD7398 Large Signal Settling Time

Figure 18. AD7398 Shutdown Recovery

Figure 19. AD7398 Multiplying Gain vs. Frequency

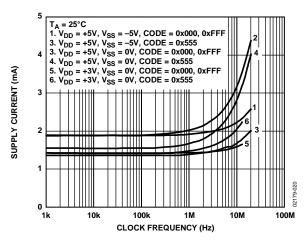

Figure 20. AD7398 Supply Current vs. Clock Frequency

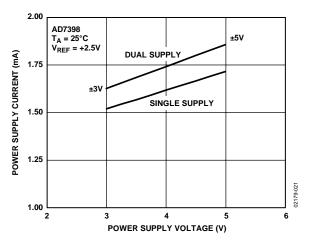

Figure 21. AD7398 Supply Current vs. Supply Voltage

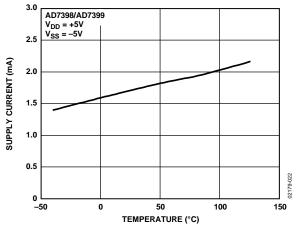

Figure 22. Supply Current vs. Temperature

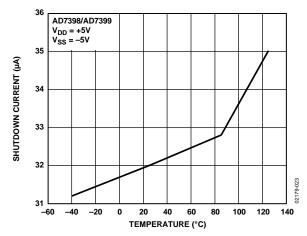

Figure 23. Shutdown Current vs. Temperature

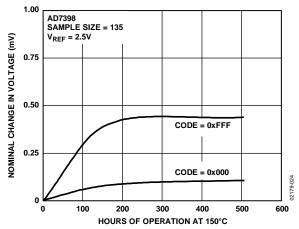

Figure 24. AD7398 Long-Term Drift

## THEORY OF OPERATION

Figure 25. Simplified Block Diagram

The AD7398/AD7399 contain four 12-bit and 10-bit, respectively, voltage output, digital-to-analog converters. Each DAC has its own independent multiplying reference input. Both the AD7398 and AD7399 use a 3-wire, SPI-compatible serial data interface, with an asynchronous  $\overline{\text{RS}}$  pin for zero-scale reset. In addition, an  $\overline{\text{LDAC}}$  strobe enables four-channel simultaneous updates for hardware-synchronized output voltage changes.

Figure 26. Simplified DAC Channel

#### **DAC OPERATION**

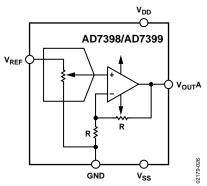

The internal R-2R ladder of the AD7398/AD7399 operates in the voltage switching mode, maintaining an output voltage that is the same polarity as the input reference voltage. A proprietary scaling technique is used to attenuate the input reference voltage in the DAC. The output buffer amplifies the internal DAC output to achieve a  $V_{\text{REF}}$  to  $V_{\text{OUT}}$  gain of unity.

The nominal DAC output voltage is determined by the externally applied  $V_{\text{REF}}$  and the digital data (D) as

$$V_{OUT} = V_{REF} \times D/4096 (For AD7398) \tag{1}$$

$$V_{OUT} = V_{REF} \times D/1024 \text{ (For AD7399)}$$

(2)

where:

D is the 12-bit or 10-bit decimal equivalent of the data word.  $V_{\it REF}$  is the externally applied reference voltage.

In order to maintain good analog performance, the user should bypass power supplies with 0.01  $\mu F$  ceramic capacitors (mount them close to the supply pins) and 1  $\mu F$  to 10  $\mu F$  tantalum capacitors in parallel. In addition, clean power supplies with low ripple voltage capability should be used. Switching power supplies can be used for this application, but beware of its higher ripple voltage and PSS frequency-dependent characteristics. It is also best to supply power to the AD7398/AD7399 from the system's analog supply voltages. Do not use the digital 5 V supply.

The reference input resistance is code dependent, exhibiting worst case 35 k $\Omega$  for AD7398 when the DAC is loaded with alternating codes 010101010101. Similarly, the reference input resistance is 40 k $\Omega$  for AD7399 when the DAC is loaded with 0101010101.

#### OPERATION WITH VREF EQUAL TO THE SUPPLY

The AD7398/AD7399 are designed to approach the full output voltage swing from ground to  $V_{\text{DD}}$  or  $V_{\text{SS}}$ . The maximum output swing is achieved when the corresponding V<sub>REF</sub> input pin is tied to the same power supply. This power supply should be low noise and low ripple, preferably operated by a suitable reference voltage source such as ADR292 or REF02. The output swing is limited by the internal buffer offset voltage and the output drive current capability of the output stage. Users should at least budget the VZSE offset voltage as the closest the output voltage can get to either supply voltage under a no load condition. Under a loaded output, degrade the headroom by a factor of 2 mV per 1 mA of load current. Also note that the internal op amp has an offset voltage so that the first eight codes of AD7398 may not respond at the supply voltage or at ground until the internal DAC voltage exceeds the offset voltage of the output buffers. Similarly, the first two codes of AD7399 should not be used.

#### **POWER SUPPLY SEQUENCING**

$V_{\rm DD}/V_{\rm SS}$  of AD7398/AD7399 should be powered from the system analog supplies. The external reference input can be supplied from the same supply to avoid a possible latch-up when the reference is powered on prior to  $V_{\rm DD}/V_{\rm SS}$ , or powered off subsequent to  $V_{\rm DD}/V_{\rm SS}$ . If  $V_{\rm DD}/V_{\rm SS}$  and  $V_{\rm REF}$  have separate power sources, ensure the power-up sequence is GND,  $V_{\rm DD}$ ,  $V_{\rm SS}$ ,  $V_{\rm REF}/digital$  input/digital output. The reverse sequence applies to the power-down sequence. The order of  $V_{\rm REF}$  and digital input/digital output is not important. In addition,  $V_{\rm REF}$  pins of the unused DACs should be connected to GND or some other power sources to ensure a similar power-up/power-down sequence.

#### PROGRAMMABLE POWER SHUTDOWN

The two MSBs of the serial input register, SA and SD, are used to program various shutdown modes. If SA is set to Logic 1, all DACs are placed in shutdown mode. If SA = 0 and SD = 1, a corresponding DAC is shutdown addressed by Bit A0 and Bit A1 (see the Input Registers section).

#### **WORST CASE ACCURACY**

Assuming a perfect reference, the worst-case output voltage can be calculated from the following equation:

$$V_{OUT} = \frac{D}{2^N} \times (V_{REF} + V_{FSE}) + V_{ZSE} + INL$$

(3)

where:

D =decimal code loaded to DAC ranges  $0 \le D \le 2^{N}-1$ .

N = number of bits.

$V_{REF}$  = applied reference voltage.

$V_{FSE}$  = full-scale error in volts.

$V_{ZSE}$  = zero-scale error in volts.

$\mathit{INL} = \text{integral nonlinearity in volts.}$  INL is 0 at full scale or zero scale.

#### **SERIAL DATA INTERFACE**

The AD7398/AD7399 uses a 3-wire ( $\overline{CS}$ , SDI, CLK) SPIcompatible serial data interface. Serial data of the AD7398 and AD7399 is clocked into the serial input register in a 16-bit and 14bit data-word format, respectively. MSBs are loaded first. The Input Registers section defines the 16 data-word bits for AD7398 and the 14 data-word bits for the AD7399. Data is placed on the SDI pin, and clocked into the register on the positive clock edge of CLK, subject to the data setup and data hold time requirements specified in the Specifications section. Data can only be clocked in while the CS chip select pin is active low. For the AD7398, only the last 16 bits clocked into the serial register are interrogated when the  $\overline{\text{CS}}$  pin returns to the logic high state, and extra data bits are ignored. For the AD7399, only the last 14 bits clocked into the serial register are interrogated when the CS pin returns to the logic high state. Because most microcontrollers output serial data is in eight-bit bytes, two right-justified data bytes can be written to the AD7398 and AD7399. Keeping the CS line low between the first and second byte transfers results in a successful serial register update.

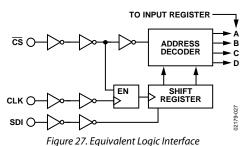

Once the data is properly aligned in the shift register, the positive edge of the  $\overline{\text{CS}}$  initiates the transfer of new data to the target DAC register, determined by the decoding of Address Bit A1 and Address Bit A0. For the AD7398, Table 5, Table 6, the Input Registers section, Figure 3, and Figure 4 define the characteristics of the serial interface. For the AD7399, Table 5, Table 6, the Input Registers section, and Figure 4 (with a 14-bit exception) define the characteristics of the serial interface. Figure 27 and Figure 28 show the equivalent logic interface for the key digital control pins for AD7398 and AD7399.

An asynchronous  $\overline{RS}$  provides hardware control reset to zero-code state over the preset function and DAC register loading. If this function is not needed, the  $\overline{RS}$  pin can be tied to logic high.

#### **POWER-ON RESET**

When the  $V_{\rm DD}$  power supply is turned on, an internal reset strobe forces all the input and DAC registers to the zero-code state. The  $V_{\rm DD}$  power supply should have a smooth positive ramp without drooping in order to have consistent results, especially in the region of  $V_{\rm DD}=1.5~V$  to 2.2 V. The  $V_{SS}$  supply has no effect on the power-on reset performance. The DAC register data stays at zero until a valid serial register data load takes place.

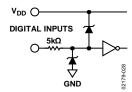

#### **ESD Protection Circuits**

All logic input pins contain back-biased ESD protection Zeners connected to ground (GND) and  $V_{\rm DD}$  as shown in Figure 28.

Figure 28. Equivalent ESD Protection Circuits

#### MICROPROCESSOR INTERFACING

Microprocessor interfacing to the AD7398/AD7399 is via a serial bus that uses standard protocol compatible with DSP processors and microcontrollers. The communications channel requires a 3-wire interface consisting of a clock signal, a data signal, and a synchronization signal. The AD7398/AD7399 require a 16-bit/14-bit data word with data valid on the rising edge of CLK. The DAC update can be done automatically when all the data is clocked in, or it can be done under control of LDAC.

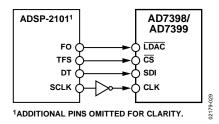

#### ADSP-2101 to AD7398/AD7399 Interface

Figure 29 shows a serial interface between the AD7398/AD7399 and the ADSP-2101. The ADSP-2101 is set to operate in the serial port (SPORT) transmit alternate framing mode. The ADSP-2101 is programmed through the SPORT control register and should be configured as follows: Internal clock operation, active low framing, 16-bit-word length. For the AD7398, transmission is initiated by writing a word to the Tx register after the SPORT has been enabled. For the AD7399, the first two bits are don't care as the AD7399 keeps the last 14 bits. Similarly, transmission is initiated by writing a word to the Tx register after the SPORT has been enabled. Because of the edge-triggered difference, an inverter is required at the SCLKs between the DSP and the DAC.

Figure 29. ADSP-2101 to AD7398/AD7399 Interface

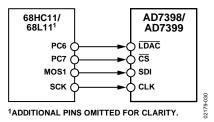

#### 68HC11/68L11 to AD7398/AD7399 Interface

Figure 30 shows a serial interface between the AD7398/AD7399 and the 68HC11/68L11 microcontroller. SCK of the 68HC11/68L11 drives the CLK of the DAC, and the MOSI output drives the serial data lines SDI.  $\overline{\text{CS}}$  signal is driven from one of the port lines. The 68HC11/68L11 are configured for master mode; MSTR = 1, CPOL = 0, and CPHA = 0. Data appearing on the MOSI output is valid on the rising edge of SCK.

Figure 30. 68HC11/68L11 to AD7398/AD7399 Interface

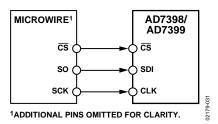

#### MICROWIRE™ to AD7398/AD7399 Interface

Figure 31 shows an interface between the AD7398/AD7399 and any MICROWIRE-compatible device. Serial data is shifted out on the falling edge of the serial clock and into the AD7398/AD7399 on the rising edge of the serial clock. No glue logic is required as the DAC clocks data into the input shift register on the rising edge.

Figure 31. MICROWIRE to AD7398/AD7399 Interface

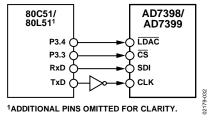

#### 80C51/80L51 to AD7398/AD7399 Interface

A serial interface between the AD7398/AD7399 and the 80C51/80L51 microcontroller is shown in Figure 32. TxD of the microcontroller drives the CLK of the AD7398/AD7399, and RxD drives the serial data line of the DAC. P3.3 is a bit-programmable pin on the serial port that is used to drive  $\overline{\text{CS}}$ .

Figure 32. 80C51/80L51 to AD7398/AD7399 Interface

Note that the 80C51/80L51 provide the LSB first, although the AD7398/AD7399 expect the MSB of the 16-bit/14-bit word first. Care should be taken to ensure the transmit routine takes this into account. This can usually be done with software by shifting out and accumulating the bits in the correct order before inputting to the DAC. In addition, 80C51 outputs two byte words/16 bits of data. Thus for AD7399, the first two bits, after rearrangement, should be don't care as they are dropped from the 14-bit word of the AD7399.

When data is to be transmitted to the DAC, P3.3 is taken low. Data on RxD is valid on the falling edge of TxD, so the clock must be inverted as the DAC clocks data into the input shift register on the rising edge of the serial clock. The 80C51/80L51 transmit their data in 8-bit bytes with only eight falling clock edges occurring in the transmit cycle. As the AD7399 requires a 14-bit word, P3.3 (or any one of the other programmable bits) is the  $\overline{\text{CS}}$  input signal to the DAC; therefore P3.3 should be brought low at the beginning of the 16-bit write cycle  $2\times8$  bit-words, and held low until the 16-bit  $2\times8$  cycle is completed. After that, P3.3 is brought high again and the new data loads to the DAC. Again, the first two bits, after rearranging, should be don't care.  $\overline{\text{LDAC}}$  on the AD7398/AD7399 can also be controlled by the 80C51/80L51 serial port output by using another bit-programmable pin, P3.4.

## APPLICATIONS INFORMATION

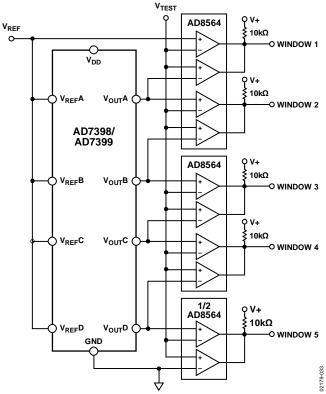

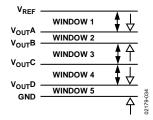

#### STAIRCASE WINDOWS COMPARATOR

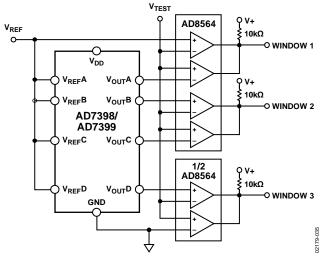

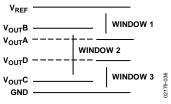

Many applications need to determine whether voltage levels are within predetermined limits. Some requirements are for nonoverlapping windows and others for overlapping windows. Both circuit configurations are shown in Figure 33 and Figure 34, respectively.

Figure 33. Nonoverlapping Windows Comparator

Figure 34. Nonoverlapping Windows Range

Figure 35. Overlapping Windows Comparator

Figure 36. Overlapping Windows Range

The nonoverlapping circuit employs one AD7398/AD7399 and ten comparators to achieve five voltage windows. These windows range between  $V_{\text{REF}}$  and analog ground as shown in Figure 34. Similarly, the overlapping circuit employs six comparators to achieve three overlapping windows (see Figure 36).

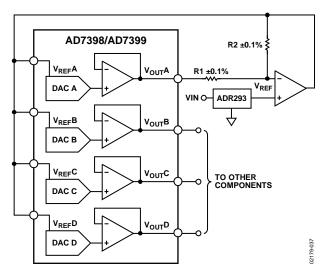

#### PROGRAMMABLE DAC REFERENCE VOLTAGE

With the flexibility of the AD7398/AD7399, one of the internal DACs can be used to control a common programmable  $V_{\text{REFX}}$  for the remainder of the DACs.

The circuit configuration is shown in Figure 37. The relationship of  $V_{\text{REFX}}$  to  $V_{\text{REF}}$  is dependent upon the digital code and the ratio of R1 and R2, and is given by

$$V_{REFX} = V_{REF} \times \left(1 + \frac{R2}{R1}\right) - V_{REFX} \times \frac{D}{2^N} \times \frac{R2}{R1}$$

(4)

$$V_{REFX} = \frac{V_{REF} \times \left(1 + \frac{R2}{R1}\right)}{\left(1 + \frac{D}{2^N} \times \frac{R2}{R1}\right)}$$

(5)

where:

D = decimal equivalent of input code.

N = number of bits.

$V_{REF}$  = applied external reference.

$V_{REFX}$  = reference voltage for DAC A to DAC D.

Table 7. VREFX vs. R1 and R2

| R1, R2   | Digital Code   | V <sub>REFX</sub>    |  |

|----------|----------------|----------------------|--|

| R1 = R2  | 0000 0000 0000 | 2 V <sub>REF</sub>   |  |

| R1 = R2  | 1000 0000 0000 | 1.3 V <sub>REF</sub> |  |

| R1 = R2  | 1111 1111 1111 | V <sub>REF</sub>     |  |

| R1 = 3R2 | 0000 0000 0000 | 4 V <sub>REF</sub>   |  |

| R1 = 3R2 | 1000 0000 0000 | 1.6 V <sub>REF</sub> |  |

| R1 = 3R2 | 1111 1111 1111 | $V_{REF}$            |  |

|          |                |                      |  |

The accuracy of  $V_{\text{REFX}}$  is affected by the quality of R1 and R2. Therefore, tight tolerance, low tempco, thin film resistors should be used.

Figure 37. Programmable DAC Reference

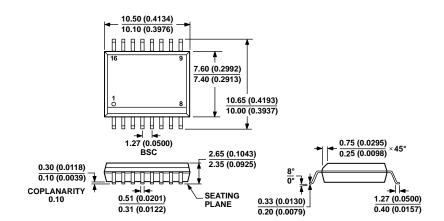

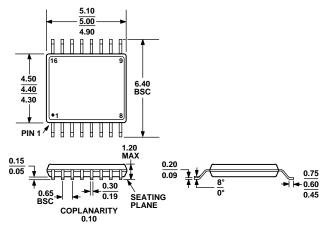

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-013-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 38. 16-Lead Standard Small Outline Package [SOIC\_W] Wide Body (RW-16)

Dimensions shown in millimeters and (inches)

COMPLIANT TO JEDEC STANDARDS MO-153-AB

Figure 39. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1, 2</sup> Resolution (Bits)                             |                  | Temperature Range   | Package Description | Package Option     | Ordering Quantity |  |

|---------------------------------------------------------------------|------------------|---------------------|---------------------|--------------------|-------------------|--|

| AD7398BR                                                            | 12               | -40°C to +125°C     | 16-Lead SOIC_W      | RW-16              | 47                |  |

| AD7398BR-REEL                                                       | .D7398BR-REEL 12 |                     | 16-Lead SOIC_W      | RW-16              | 1,000             |  |

| AD7398BRZ                                                           | 12               | −40°C to +125°C     | 16-Lead SOIC_W      | RW-16              | 47                |  |

| AD7398BRZ-REEL                                                      | 12               | -40°C to +125°C     | 16-Lead SOIC_W      | RW-16              | 1,000             |  |

| AD7398BRU                                                           | 12               | -40°C to +125°C     | 16-Lead TSSOP       | RU-16              | 96                |  |

| AD7398BRU-REEL7                                                     | 12               | -40°C to +125°C     | 16-Lead TSSOP       | RU-16              | 1,000             |  |

| AD7398BRUZ                                                          | 12               | -40°C to +125°C     | 16-Lead TSSOP       | RU-16              | 96                |  |

| AD7398BRUZ-REEL7                                                    | 12               | -40°C to +125°C     | 16-Lead TSSOP       | RU-16              | 1,000             |  |

| AD7398WBRUZ-RL7                                                     | 12               | -40°C to +125°C     | 16-Lead TSSOP       | RU-16              | 1,000             |  |

| AD7399BR                                                            | 10               | -40°C to +125°C     | 16-Lead SOIC_W      | RW-16              | 47                |  |

| AD7399BR-REEL                                                       | 10               | -40°C to +125°C     | 16-Lead SOIC_W      | RW-16              | 1,000             |  |

| AD7399BRZ 10                                                        |                  | −40°C to +125°C     | 16-Lead SOIC_W      | RW-16              | 47                |  |

| AD7399BRZ-REEL                                                      | 10               | -40°C to +125°C     | 16-Lead SOIC_W      | RW-16              | 1,000             |  |

| AD7399BRU                                                           | 10               | -40°C to +125°C     | 16-Lead TSSOP       | RU-16              | 96                |  |

| AD7399BRU-REEL7 10 -40°C to +125°C<br>AD7399BRUZ 10 -40°C to +125°C |                  | 16-Lead TSSOP RU-16 |                     | 1,000              |                   |  |

|                                                                     |                  | -40°C to +125°C     | 16-Lead TSSOP       | 5-Lead TSSOP RU-16 |                   |  |

| AD7399BRUZ-REEL7                                                    | 10               | -40°C to +125°C     | 16-Lead TSSOP       | RU-16              | 1,000             |  |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

The AD7398 contains 3254 transistors. The die size measures 108 mils  $\times$  144 mils.

#### **AUTOMOTIVE PRODUCTS**

The AD7398WBRUZ-RL7 model is available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that this automotive model may have specifications that differ from the commercial models; therefore, designers should review the Specifications section of this data sheet carefully. Only the automotive grade product shown is available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for this model.

$<sup>^{2}</sup>$  W = Qualified for Automotive Applications.

| ٨ | U. | 73 | a  | Q | // | U. | 72 | a  | 0  |

|---|----|----|----|---|----|----|----|----|----|

| н | U. | ΙJ | IJ | U | m  | U  | ΙJ | IJ | IJ |